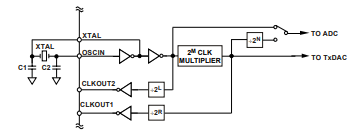

AD9865BCPZ представляет собой высокоинтегрированный MxFEICдля приложений приемопередатчиков, требующих функциональности канала передачи и приема. Разработанный для приемопередатчиков, требующих скорости передачи данных до 80 MSPS, он объединяет возможности передачи и приема. Он предлагает гибкий цифровой интерфейс, режимы энергосбережения и высокую изоляцию передачи и приема. Гибкий цифровой интерфейс, режимы энергосбережения и высокая изоляция передачи и приема делают его идеальным для полудуплексных и полнодуплексных приложений. Цифровой интерфейс отличается высокой гибкостью и обеспечивает прямое подключение к цифровым серверным модулям, поддерживающим полудуплексную или полнодуплексную передачу данных. Обычно это позволяетAD9865BCPZдля замены дискретных решений АЦП и ЦАП. Встроенные умножители тактовой частоты и синтезаторы PLL обеспечивают все необходимые внутренниечасы, а также два внешних синхроимпульса от одного кварцевого генератора или источника тактовых импульсов.

AD9865BCPZBCPZ Подробности

| Артикул | Производитель | Техническая спецификация | Запас | распределитель | Цена | Контакт |

| AD9865BCPZ | Аналоговые устройства Inc. | Техническое описание AD9865BCPZ | 15000 | НИЦ Электроника | Обновление | sales@sic-comComponents.com |

AD9865BCPZBCPZФункции

Недорогой КМОП MxFETM 3,3 В для широкополосных модемов 10-битный цифро-аналоговый преобразователь 2×/4× интерполяционный фильтр

Скорость обновления ЦАП 200 MSPS

Встроенный линейный драйвер 23 дБм с регулировкой усиления 19,5 дБ 10-битный аналого-цифровой преобразователь, 80 MSPS

От −12 дБ до +48 дБ малошумящий RxPGA (< 3,0 нВ/rtГц)

Программируемый фильтр нижних частот третьего порядка.

Гибкий интерфейс передачи цифровых данных

Полу- и полнодуплексный режим

Обратная совместимость с AD9975 и AD9875.

Различные режимы отключения/снижения мощности

Внутренний умножитель тактовой частоты (PLL)

2 вспомогательных программируемых тактовых выхода

Доступен в корпусе с 64 выводами или в корпусе с голым кристаллом.

Характеристики тракта передачи сигнала AD9865BCPZ

Путь передачи сигнала включает в себя обходной интерполяционный фильтр нижних частот 2x/4x, 10-битный TxDAC и линейный драйвер.

Полоса пропускания сигнала тракта передачи достигает 34 МГц при скорости входных данных 80 MSPS.

TxDAC обеспечивает выходной дифференциальный ток, способный напрямую управлять внешними нагрузками или внутренними усилителями тока с низкими искажениями.

Усилитель тока (IAMP) может быть сконфигурирован как линейный драйвер тока или напряжения (с использованием двух внешних NPN-транзисторов), способный выдавать пиковую мощность сигнала более 23 дБм.

Мощность передачи контролируется цифровым способом в диапазоне 19,5 дБ с шагом 0,5 дБ.

Характеристики пути прохождения сигналаAD9865BCPZ

Тракт приема сигнала включает усилитель с программируемым усилением (RxPGA), регулируемый фильтр нижних частот (LPF) и 10-битный АЦП.

Малошумящий RxPGA имеет программируемый диапазон усиления от -12 дБ до +48 дБ с шагом 1 дБ.

При настройках усиления, превышающих 36 дБ, входной опорный шум составляет менее 3 нВ/√Гц.

Частоту среза ФНЧ приемного тракта можно установить в диапазоне от 15 МГц до 35 МГц или просто обойти.

10-битный АЦП обеспечивает превосходные динамические характеристики в диапазоне от 5 до 80 MSPS.

И RxPGA, и АЦП обеспечивают масштабируемое энергопотребление, что позволяет оптимизировать энергопотребление и производительность.

Источник питания и цифровые характеристики дляAD9865BCPZ

Характеристики источника питания AD9865BCPZ включают ток аналогового питания, ток цифрового питания и общий ток питания.

В дуплексном режиме общий ток питания составляет от 406 до 475 мА.

Потребление энергии также снижается в полудуплексном режиме: от 112 до 130 мА в режиме передачи и от 225 до 253 мА в режиме приема.

Потребляемая мощность функциональными блоками включает RxPGA и LPF, ADC, TxDAC, IAMP (программируемый), опорный сигнал, тактовую систему PLL и синтезатор.

Максимально допустимая потребляемая мощность составляет 1,66 Вт при общем токе питания 13 мА в режиме ожидания.

Цифровой интерфейс и временные характеристики дляAD9865BCPZ

Характеристики логического входа и выхода КМОП, включая высокое входное напряжение, низкое входное напряжение, входной ток утечки, входную емкость и т. д.

Время нарастания/спада выходного сигнала указано для различных условий нагрузки.

Минимальная ширина импульса сигнала сброса составляет один тактовый цикл.

Характеристики времени записи последовательного порта, включая тактовую частоту SCLK, высокое время тактового сигнала SCLK, низкое время тактового сигнала SCLK и т. д.

Области применения и техническая поддержка AD9865BCPZ

Используется в сетях линий электропередачи, VDSL, HPNA и других областях. Техническая поддержка доступна через веб-сайт Analog Devices, что гарантирует получение пользователями своевременной технической помощи и ресурсов.

AD9865BCPZКатегория чипа:

Сопутствующие товары:

AD9515BCPZ AD9865BCP AD9515BCPZ AD9745BCPZ

AD9265BCPZ-125 AD9265BCPZ-105 AD9866BCPZ AD9869BCPZ

AD9965BCPZ AD9867BCPZ AD9864BCPZ

Список желаний (0 шт.)

Список желаний (0 шт.)